By Alan High, Technical Director

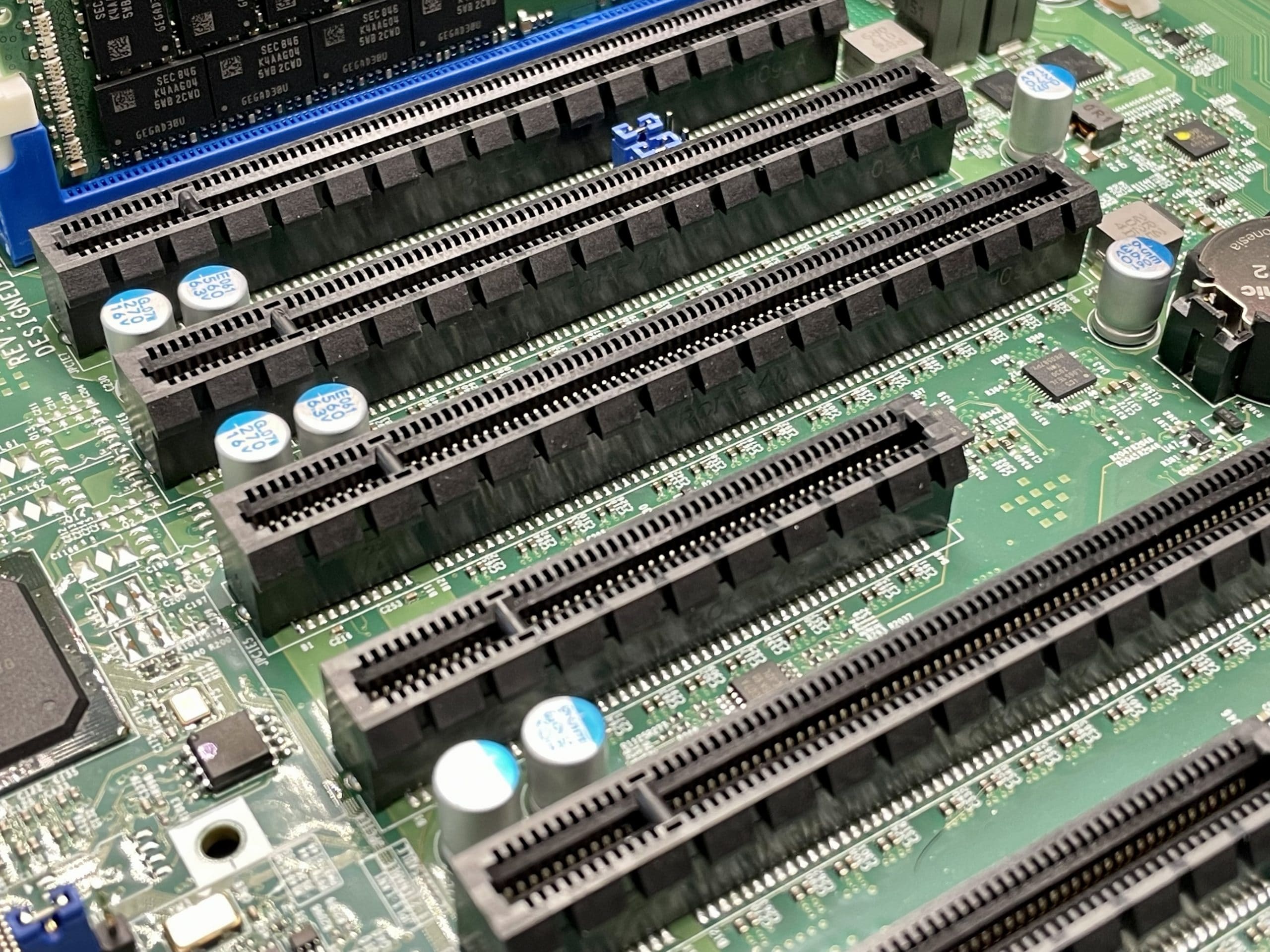

PCIe is a point-to-point serial data bus that delivers information from one component to another at extremely high data rates. Using advanced data encoding techniques, it can transmit many gigabits per second via a single pair of wires. It is designed to scale for increased bandwidth by aggregating multiple connections, or lanes, in parallel. Lane widths of x1, x4, x8 and x16 are most common and the bandwidth available with each expansion scales linearly. Intended as a replacement for older buses such as ISA and PCI, PCIe has not only kept pace with technological advancements in bandwidth, it is on the verge of consuming many existing computer interconnects such as SATA, SAS and—most interestingly—USB.

PCIe is the underlying technology behind the high-speed storage interface NVMe (non-volatile memory express), which is replacing SAS and SATA as the flash storage interconnect bus of choice in modern equipment. In essence, NVMe is taking advantage of the PCIe’s increased speed and scalability by connecting flash storage directly to the CPU’s PCIe bus. In turn, this grants NVMe-connected storage devices a massive boost in throughput. Unfortunately, CPUs have had a difficult time keeping pace with the increased demand for PCIe lanes, especially in data centers where there may be dozens of storage devices per CPU. To address this issue, large installations may employ PCIe switches that work much like a network switch to effectively split a small number of PCIe lanes into more at the expense of per-lane throughput. Host bus adapters and RAID controllers can be used in a similar fashion and may provide additional capabilities, such as backplane awareness and redundancy.

One of the more interesting new PCIe applications is in the newest USB revision, USB4. Announced in 2019, USB4 is now beginning to appear in new products. USB4 retains the USB-specific signaling of prior generations, but adds a new mode that can connect the device directly to the PCIe bus. This provides up to 40Gbps connectivity, which increases achievable transfer rates for traditional USB uses, like removable storage, and enables some novel technologies that weren’t possible with previous generations. For example, laptop docking stations equipped with multiple full-bandwidth slots should now be possible and AR/VR headsets may no longer require a direct GPU connection.

As PCIe becomes the default for high-speed interconnect, PCIe Gen4 is on the cusp of widespread use. Gen4 doubles the speed from Gen3, providing nearly 2GB/s per lane. This allows for multi-port 100GbE or 200GbE network interfaces and the ability to connect incredibly powerful GPUs, FPGAs and other peripherals with more bandwidth than ever, enabling innovative new uses and massively increased performance.

However, as speeds double, power and heat increase, and signal integrity becomes harder to maintain. Designing PCIe Gen4 devices for use in harsh environments represents a significant challenge when environmental hardening is also required. Traditional locking military circular connectors do not deliver sufficient performance for transporting signals at these speeds, so novel connector technologies must be employed. Thermal approaches need to be reconsidered to effectively manage the greater heat output and internal cabling used for prior generations may need to be updated given the more stringent signal integrity requirements. That’s why we’re already tackling these critical challenges. We want to ensure our customers are equipped to use and benefit from PCIe Gen4’s expanded capabilities for seamless, accurate performance in the most demanding edge environments.

As industry becomes more reliant on computing technology and continues to demand more capable technologies in the system integration stage, applications and users will reap the benefits of remarkable connectivity in smaller form factors and over longer distances. As PCIe Gen4 continues to take over more backend interconnect technology used by modern computers, don’t get too comfortable with this iteration—PCIe Gen5 is just around the corner.